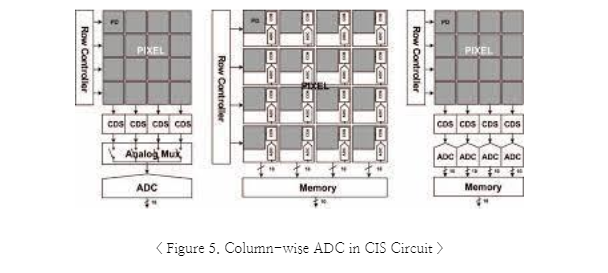

Basically, CIS utilizes the Column-parallel ADC Architecture, which processes data with one long ADC per column. Unlike a typical layout, the CIS layout is done in a unique way to put all ADCs in a very small pitch of about 1um. The most layout uses Dummy correctly, has a differential structure, or applies various techniques such as Common-centroid to prevent mismatch, but CIS Layout is designed in order of Mismatch due to limited space. A typical type of ADC included in such a column-parallel ADC is a Single Slope ADC or an Integrated ADC. The Single Slope ADC has the simplest structure among ADCs, and as described above, it is difficult to borrow other ADC structures due to pitch limitations. In fact, the department wanted to apply DSM ADC but compared to various design problems and performance, it does not show much difference from Single Slope ADC and needs to redesign all other existing blocks, so Single Slope ADC is used for mass production products.

This Single Slope ADC extracts data by comparing Analog Ramp formed in Digital Code and DAC through a comparator and Correlated Double Sampling (CDS Operation) to compensate the lots of mismatch as aformentioned. The DAC, i.e., Ramp Generator, that generates the Analog Ramp used in these comparisons must also be accurately designed to work properly without errors. In addition, RMP can act as various functions such as analog gain control or ADC saturation level adjustment, so accurate design is required. Rather than improving the performance of this Ramp Generator, this project proceeded to understand Ramp Block by studying the principles and performance factors of the Ramp and analyzing existing designed circuits and simulations.

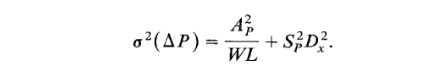

The indicator that can confirm the performance of the Ramp Generator is greatly related to Linearity. INL and Gain Linearity are typical examples. Furthermore, Horizontal Noise through Noise Analysis is another example of Ramp performance indicators. Factors that determine INL performance include Voltage Coefficient, Output Impedance, Bias Point Variation, Current Mismatch, Power IR Drop, and Parasitic Resistance. In general, the Voltage Coefficient is known as the most dominant factor, but as a result of the simulation conducted in this project, Code Nonlinearity by Current Mismatch occurred the most. This method of reducing Current Mismatches can be solved by increasing Chip Sizing as discussed in the previous REF Block. However, this method has a trade-off with Output Impedance, so the sizing should be adjusted at an appropriate rate.

In addition, when we see the equation, we can solve the problem by reducing AVth, and in order to reduce AVth, it can be designed by splitting the Transistor Length.

The most dominating factor in determining Gain Linearity is the voltage coefficient (VC) characteristics of Parasitic Resistance and polyresistance. Because Gain Linearity is obtained with each gain value, it is highly dependent on Parasitic Resistance in contrast to INL. In order to solve the parasitic resistance problem of the Resistor array, a mesh routing technique is used. And to improve the VC Char performance, a method of increasing the length of the Resistor is used.

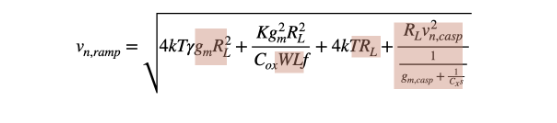

Horizontal noise is basically noise, so it requires noise analysis. When calculating the noise equation of the ramp output, it has the following values:

Based on this equation, the following design techniques can be used to reduce noise. First, it can be seen that the overall equation is proportional to Load Resistance, which can be seen that the R_L value can be reduced. In addition, to reduce current noise, increase the size of the Bias Transistor, and to reduce CASP noise, use a low noise amplifier or a Bias sampling circuit. In addition, noise can be reduced by increasing VDDA, or Nominal Voltage, to reduce noise in the first two terms, and increasing VDDA also increases Vod, which can reduce current noise by causing a decrease in gm.

The change in Horizontal Noise Portion following the Ramp Gain is also interesting. Showing that the noise formed by the Ramp Block is dominant in x1 Gain, but the noise formed by the Ramp Block in High Gain, i.e., x16 Gain, is dominant. It is expected to be a good indicator to refer to when proceeding with the design according to the change of noise portion.